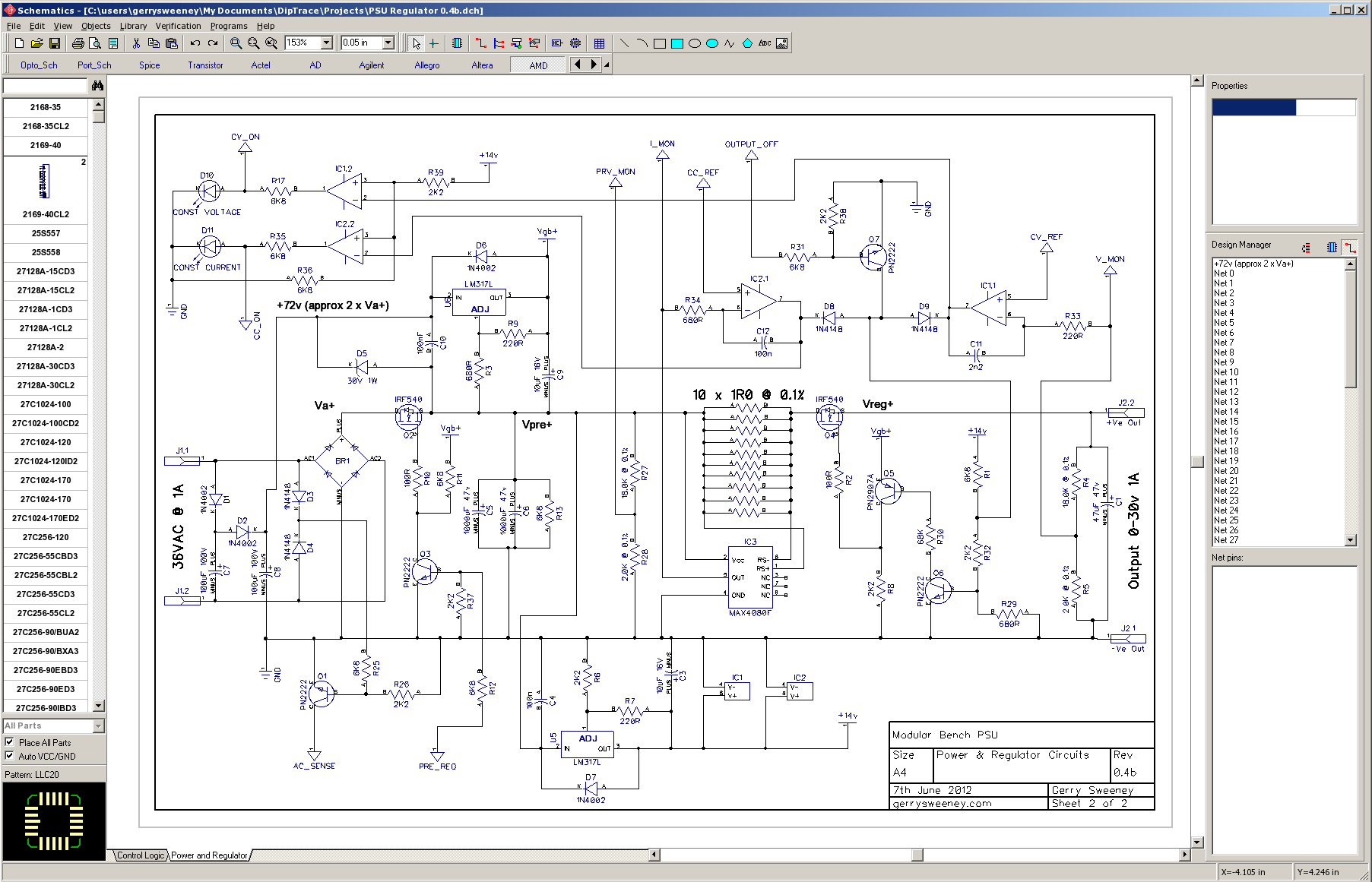

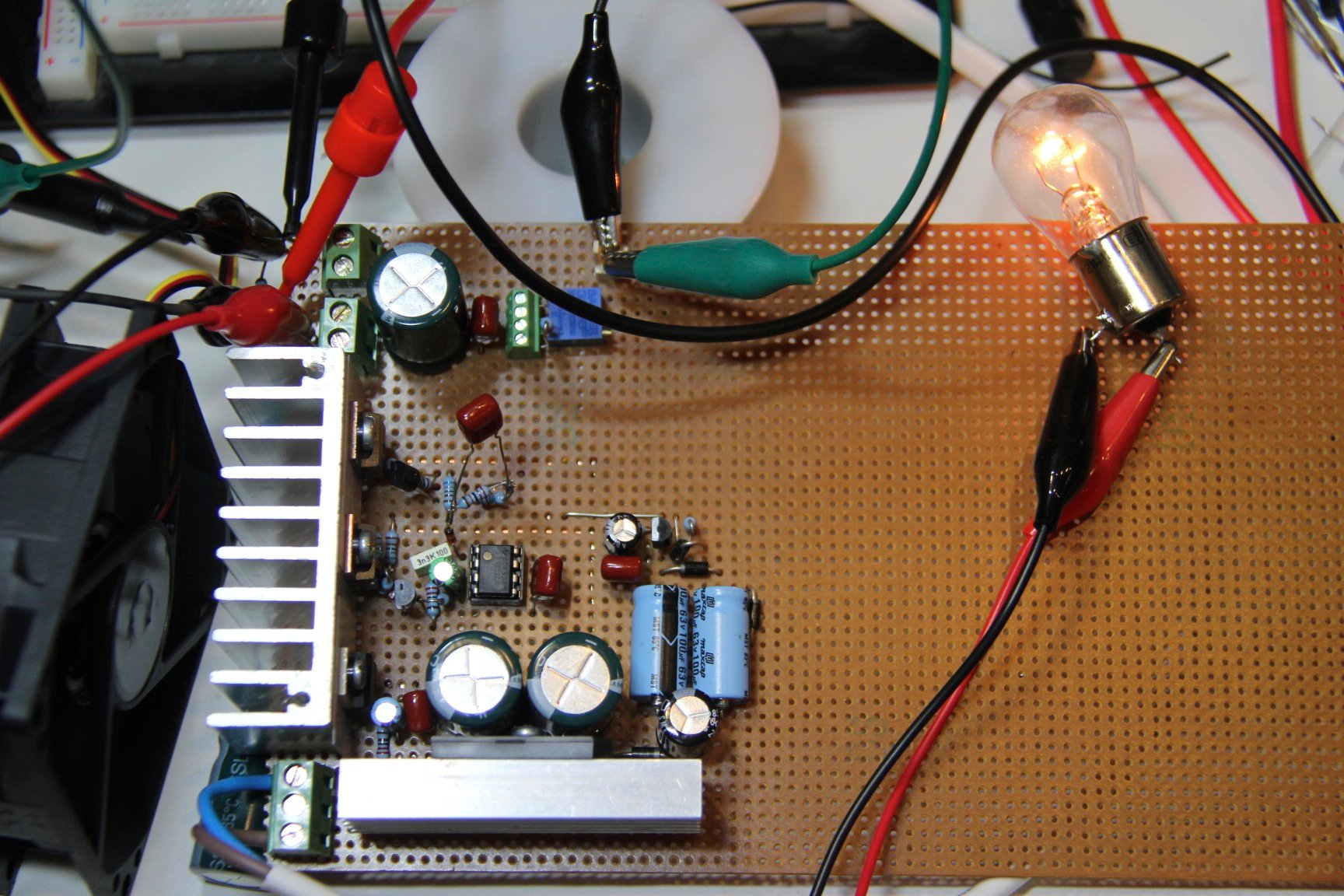

I have recently been using Diptrace for schematic capture and have just hit the 300 pin limit so I am looking at my options including alternative packages. Why am I looking at options? Having read numerous forums and reviews, based on other peoples experience it would appear that Diptrace is an improvement over Eagle and other low end solutions, I have tried Eagle In the past and I would have to agree, but Diptrace far from perfect, in fact its so poor in some areas I am now thinking about sinking time into evaluating other applications. Perhaps the EDA/CAD world has lower expectations that I do but even Diptrace which would appear to be the more intuitive of the bunch, the user interface, and more specifically the usability really sucks, it could be Sooooooooo much better.

First of all, Mac OSX support. They claim it runs on Windows and OSX which is true. But on OSX its actually running the Windows version of the software under a windows emulator called WINE. Worse than that, WINE runs under Quarts X11 which is yet another layer of abstraction before it hits the actual screen. Trust me, the thing is crappy, actually bad enough that I want to use it in Windows instead, which is tearing me away from my beloved MAC. Integration into the Mac is non-existent, files and folder structures are ten folders deep as the WINE emulator creates a Windows-like folder structure. Novram should be ashamed of their claims of OSX support, its really terrible. The software also randomly hangs which causes work to be lost, the UI is slow and cumbersome and the keyboard shortcuts sometimes stop working so you are restricted to right-mouse context menus for cut/copy/paste delete until they magically come back from time to time. So if you are going to use Diptrace, use it on Windows not a MAC. If you have a Mac, install Oracle’s virtual box, run a copy of Windows 7 and use it as a native Windows app (I am going to give DipTrace one more try under Windows to see how I go).

In terms of the hanging, they have actually added a menu option called “Recover Schematic” which mostly gets back your last changes. They have added this at some point I imagine to deal with the fact that the software is buggy and can crash/hang. It would have been better to improve the software so it never needed an option to “recover” anything…

Now onto the features of software. I have to say at this point, I don’t much like CAD software, it all seems to have “its own way” of working, seemingly much of this is a hangover from Autocad which was made before a mouse was even commonplace, so lots of strange keyboard shortcuts etc. DT reacts strangely to the mouse mostly so while people seem to think its intuitive I can only imagine other packages must really be bad. If you are used to using Windows or Mac UI’s and you have not had any CAD experience then DT will feel alien and it has a long learning curve to get you past that. I have used it (schematic capture) to create a project and it does work once you get to understand its oddities. Being a software guy I know how easy it would be to make considerable usability improvements with little effort which makes it all the more frustrating – I first came across DT about four years ago and I have to say its not really moved on from then, and that is even more frustrating. The lack of development progress and the poor usability does not say a great deal for Novram.

Here are my top 10 specific bugbears…

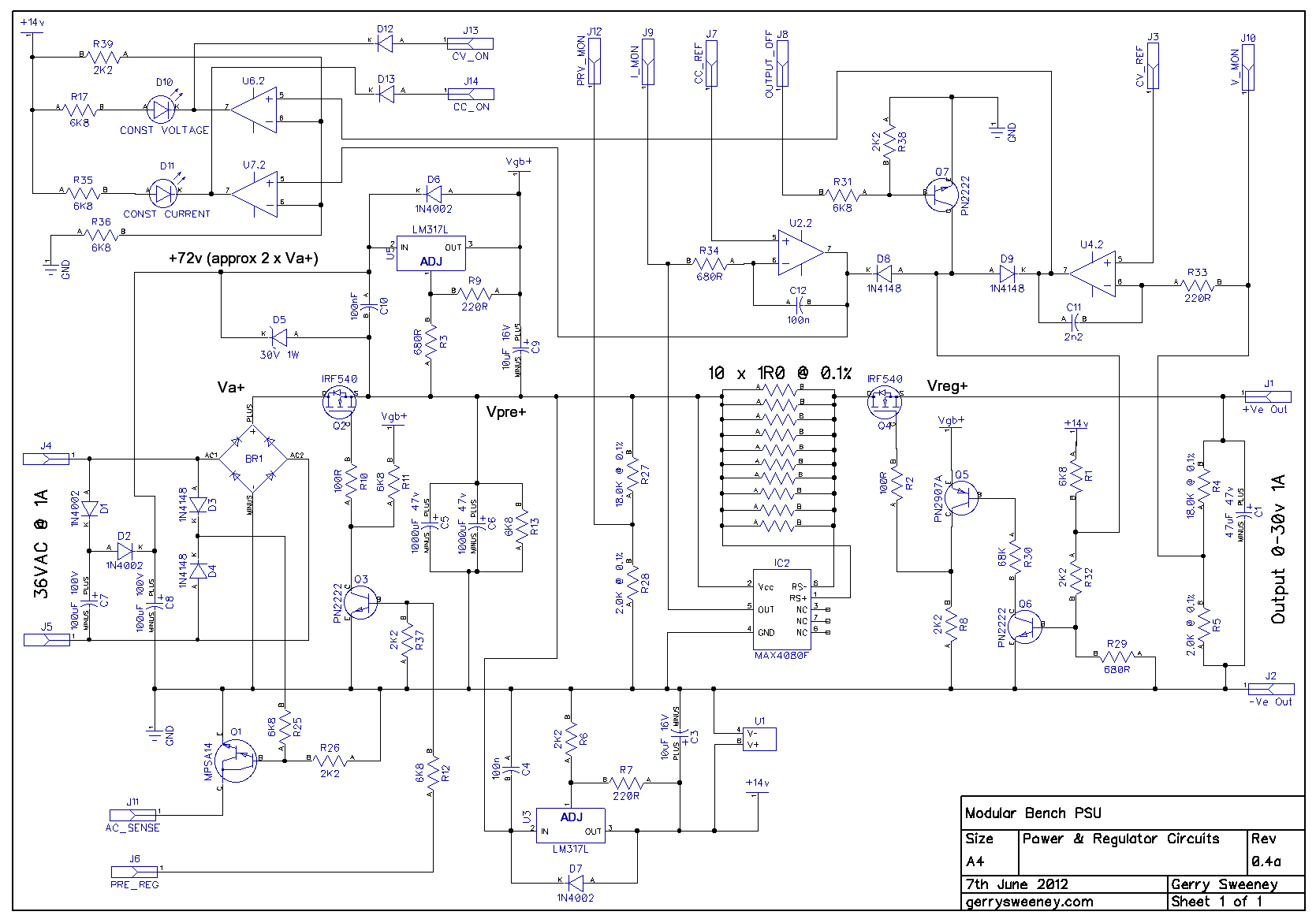

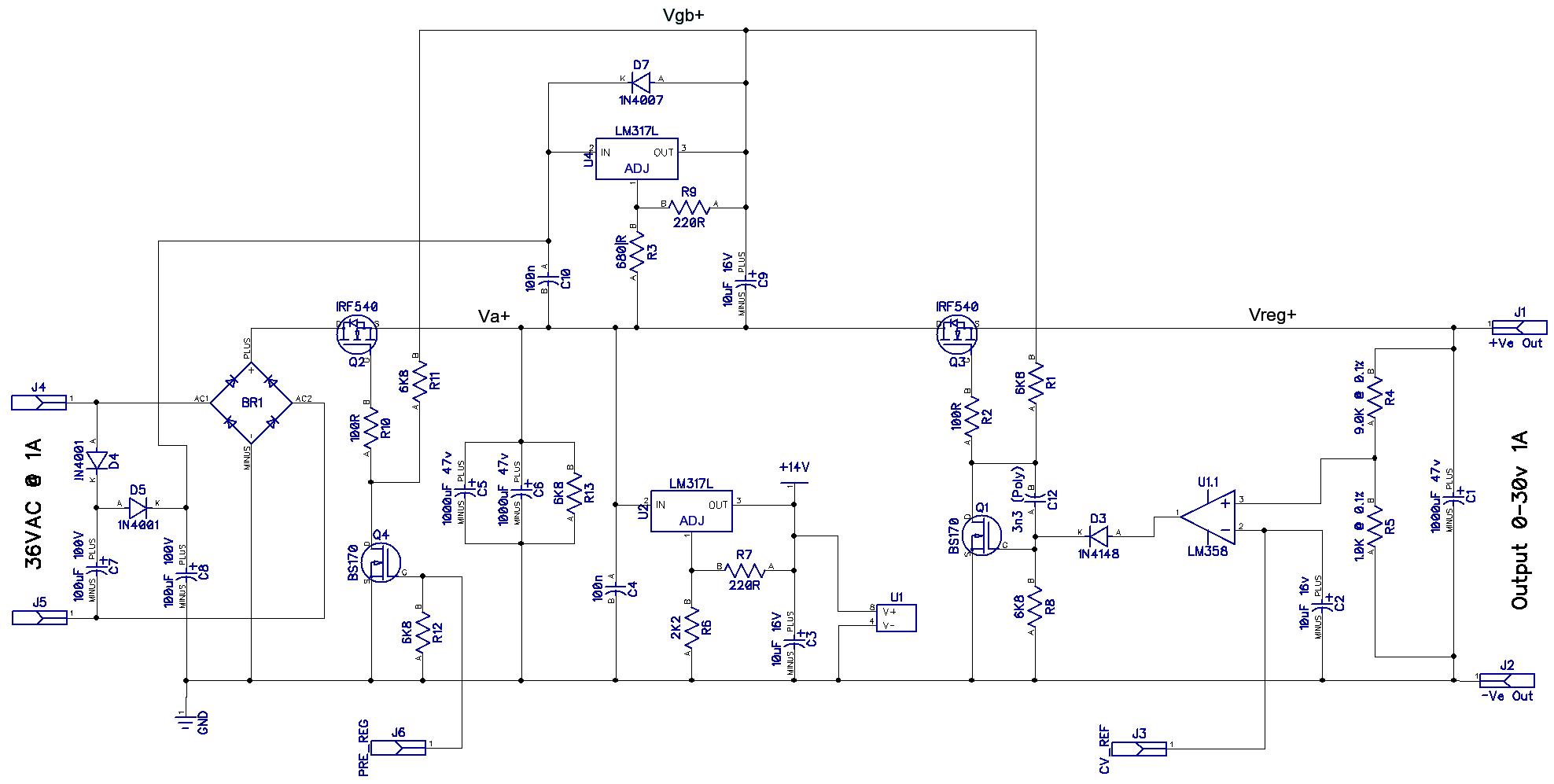

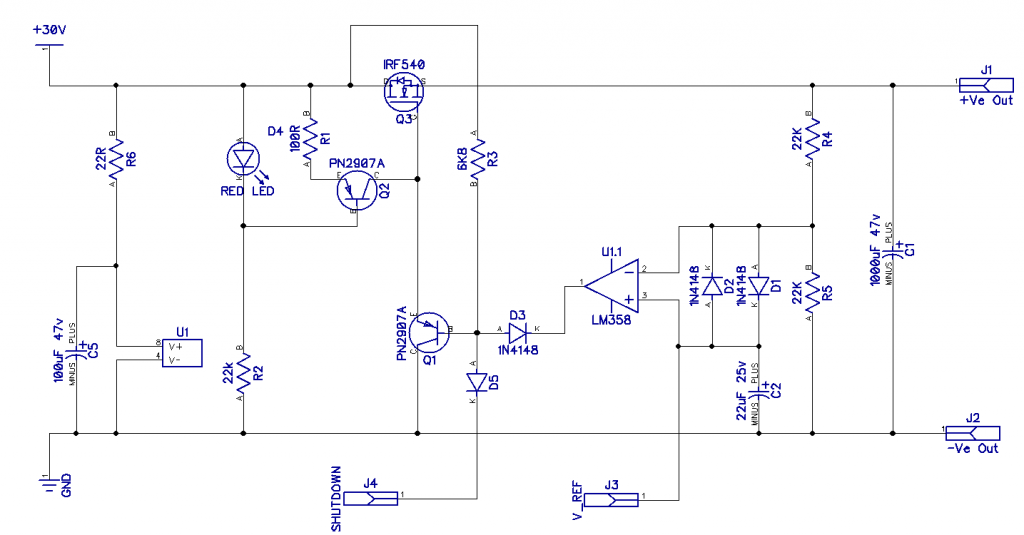

1. No control over what component elements get displayed or printed. For example, on screen I see the pin names (B,C E) for the Discrete/NPN item, or A/B on the RES item, I don’t want to see them but I can’t turn them off without also turning off the pin numbers for IC parts which I do want to see. Any electronics engineer knows which pin is the emitter of a transistor, displaying E is ridiculous. Control of this should be a properly of the part not a global view property, although you might want that too.

2. Netports appear in the BOM, I have to manually remove them from the BOM after the export to a file, there would appear to be no way to control this. It would appear that NetPorts are just another 1-pin component which is why this happens, perhaps a simple attribute on the component property called “Exclude from BOM” might help.

3. The sheet connectors are stupid, Place one and it defaults to place a bus, try to place a wire and it sort of works but the wire does not align correctly. Strange behaviour….So don’t use “Sheet Connectors” to connect your circuits across sheets, use NetPorts instead – obvious really – NOT!

4. The library selectors on the toolbar are a little odd, the names are untidy, just a lack of attention to detail. Why call something that will be displayed in the UI Con_Sch, thats the sort of name you would expect to see in code, not presented to a user. Once you select a library you get the components down the left-hand side to select from – scroll up and down this enough selecting items (as you do when you are finding your way around the libraries) and you will get it to hang the whole program. Clicking an item puts you into place mode meaning you have to press escape if you were just browsing. Right click also cancels it but you also get a right click context menu. The little drop down on the library bar drops down a scroll bar so you can scroll through the library buttons – this compensates for a poor UI design making it even more unusual. The software could do with a decent library browser and some better organisation for the actual libraries. Trying to manage parts, copying between libraries etc, all very confusing and counter intuitive.

5. Create multiple sheets which is great, but then you want to change the oder of the sheets to more logically represent the flow of your project. Tough, you just can’t do that – at least I have not found a way so far.

6. A “Save All” button would be nice….instead of having to go to each sheet and save it separately.

7. There is a need for much better schematic annotation. Single line text is really not good enough. Ideally multi-line post-it style boxes would be good.

8. When drawing a schematic with a large IC you need to be able to re-organise the pins on the component to suit the schematic you are drawing – there is no option to do this apart from create your own library, copy the part into it and re-organise it for your specific schematic….rubbish….

9. Ever hear of smooth drawing using anti-alias? No! – neither have Novram – you could argue this is not needed but I would say if you are going to stare the the thing for hours on end you want it to be easy/soft on the eye – you could argue that it will make things slower – all true but I would still like to see my creation looking nicer.

10. Float the mouse over a connection and see the net highlight – nice – what about across sheets? Nothing doing, leaving you to manually check the net names to make sure your schematic has integrity across sheets. I thought computers were meant to make less work – not more (Microsoft, please take note of this point too..)

All in all it does work and its alright I suppose but after serious use I am left with a compelling desire to find an alternative – why is that, I don’t have the same feeling after using my e-mail program or my word processor. All of the pro’s seem to favour Altium designer http://www.altium.com/ but I can not bring myself to spend $3000+ for a piece of software that is really overkill for my limited use…I would love to evaluate it one day though – not sure Altium would want me to 🙂

I am about to try AutoTRAX DEX, you can find it here http://kov.com/. I bought this about four years ago and Oh-my-god, it was the most buggy and terrible piece of software I could ever imagine. It was cheap enough though that I did not loose any sleep over it when I just chalked it up to experience and uninstalled it. The author was defensive and it was pretty clear things were not going to get addressed and it was even more abundantly clear with the very regular, sometimes daily releases that there was absolutely no quality control, one new fix and another things broken etc, I gave up after a couple of weeks. At the time the guy developing it was focused on this next generation written in .NET and an all new design, this is now 4 years in the making and I recently had another go with it. On the back of a 20 minute play around I went and paid $49 and renewed the licence I already had.

I will evaluate AutoTRAX and write a detailed review with what I find. At a glance I can say is that a lot of attention to detail when it comes to look and feel, the schematics look really nice, they print well and the component libraries appear to be reasonably comprehensive. If it works well I think it could be a good contender for Diptrace, its a lot cheaper too, $99 for totally unlimited pins, layers etc…has 3D rendering and so on….